# Area-Selective Deposition to Enable Single-digit nm Fabrication

## 2019 CNF REU Intern: James M.H Tran

# 2019 CNF REU Intern Affiliation: Electrical Engineering, The University of Texas at Dallas

CNF Project: 2019 Cornell NanoScale Science & Technology Facility Research Experiences for Undergraduates Program CNF REU Principal Investigator(s): Prof. James R. Engstrom, Chemical and Biomolecular Engineering, Cornell University CNF REU Mentor(s): Taewon Suh and Colleen C. Lawlor, Chemical and Biomolecular Engineering, Cornell University Primary Source of CNF REU Funding: National Science Foundation via

the National Nanotechnology Coordinated Infrastructure (NNCI) Grant No. NNCI-1542081

Contact: tranj@utdallas.edu, jre7@cornell.edu, ts695@cornell.edu, ccl233@cornell.edu Website: http://cnf.cornell.edu/education/reu/2019

Primary CNF Tools Used: Photolithography spinners and hot plates, GCA AS200 stepper, Oxford 81/82 (80+) RIE etchers, Anatech resist strip, CVC SC4500 e-beam evaporator (odd), Logitech Orbis CMP

#### Abstract:

As semiconductor manufacturing approaches single-digit nm feature sizes, there is an increasing difficulty in reliably patterning critical device features. A major obstacle is that conventional top-down techniques suffer from issues with alignment of device features during the manufacturing process. Area-selective deposition (ASD) seeks to remedy this by a bottom-up technique; selectively depositing films only on defined growth areas and not on non-growth regions, creating a "self-aligned" feature. We produce line and space patterned wafers of metal and dielectric, copper and silicon dioxide in this study, to serve as a substrate for ASD experiments. We use various characterization techniques, such as optical microscopy and scanning electron microscopy (SEM), to evaluate our wafers. We also discuss intended uses of these wafers in ASD experiments.

## Introduction:

For decades, top-down manufacturing has been the method of choice for fabricating semiconductor devices. However, as we approach single-digit nm feature sizes, device patterning becomes problematic. At this scale, pattern misalignment can severely affect device functionality and operation. This misalignment is known as the "edge placement error" [1], which is defined as the distance between the actual and intended position of a patterned feature. ASD could achieve device patterning at the single-digit nm scale by utilizing a bottom-up approach, selectively depositing thin films using atomic layer deposition (ALD) or chemical vapor deposition (CVD) on defined deposition areas. By depositing thin films only on intended areas, any possibility of misalignment could be eliminated, because a "self-aligned" feature is created. In addition to resolving feature misalignment, ASD also introduces advantages such as uniform, conformal, and Angstrom level thickness controlled deposition of thin films.

In this study, 10, 5, 3, and 1  $\mu$ m line and space patterns of Cu and SiO<sub>2</sub> were fabricated to study ASD of thin films. Alternating metal and dielectric patterns allow investigation of ASD of thin films on Cu and not on SiO<sub>2</sub>, or vice versa. Variable widths of Cu and SiO<sub>2</sub> enable study of how film growth varies with different feature sizes.

The pattern also has equal line and space widths of Cu and  $SiO_2$ , producing a 50/50 area coverage of metal and dielectric for *in situ* x-ray photoelectron spectroscopy (XPS) studies.

### **Experiment Details:**

500 nm SiO<sub>2</sub> on 100 mm Si wafers were utilized. Wafers were cleaned in a Hamatech automated wafer processer with piranha solution before spin coating. Brewer Science WiDE-C 15C bottom anti-reflective coating (BARC) was spun at 3000 RPM for 60 seconds before a two-step bake on a 190°C proximity hotplate for 60 seconds, followed by a 160°C vacuum hotplate for 60 seconds. OiR 620-7i photoresist was spun at 5000 RPM for 60 seconds followed by a pre-exposure 90°C vacuum hotplate bake for 60 seconds. Exposure was performed on a GCA AS200 stepper, followed by a post-exposure bake on a 115°C vacuum hotplate. Etching was performed using the Oxford 80+ reactive ion etcher. BARC was etched using an O<sub>2</sub> and Ar mixture for six minutes. SiO<sub>2</sub> was etched with a mixture of CHF<sub>3</sub> and Ar for 6:30 minutes to etch  $\sim$ 220 nm into the SiO<sub>2</sub>. Resist and BARC were stripped using an Anatech O<sub>2</sub> plasma dry strip, followed by a piranha clean. A CVC SC4500 e-beam evaporator was then used to deposit 25 nm of Ta as an adhesion layer, followed by

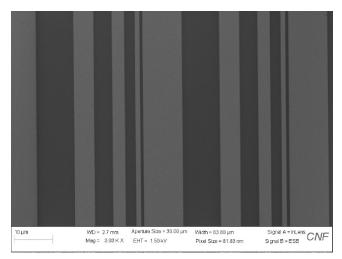

Figure 1: Top-down optical microscope image of 10, 5, 3, and 1  $\mu$ m widths of Cu and SiO<sub>2</sub>, Bright areas correspond to Cu and dark blue to SiO<sub>2</sub>.

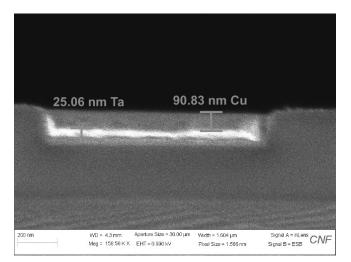

Figure 2: Cross-sectional SEM image of a 1  $\mu m$  width trench filled with 90.83 nm Cu on top of 25.06 nm Ta.

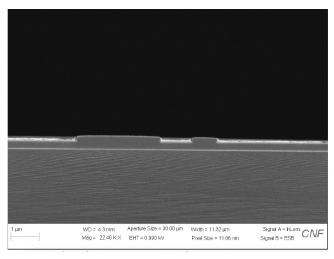

Figure 3: Etch uniformity across varying feature sizes.

300 nm Cu. Logitech-Orbis CMP was finally used to planarize the surface and remove Cu overburden at 4 psi down and 30 psi back pressure for 1:50 minutes. A Hamatech was then used again to clean the wafer of CMP debris.

## **Results and Discussion:**

Optical microscope images showed a definite line and space pattern of Cu and SiO<sub>2</sub>. Images confirm enough Cu overburden was polished away to reveal the desired pattern, as shown in Figure 1. Cross-sectional SEM images show the anisotropic etch profile, and the Cu and Ta layers deposited in Figure 2. Ta was deposited as an adhesion layer between the Cu and the SiO<sub>2</sub>. Without Ta, Cu would rip out of the trenches during the CMP step due to its poor adhesion to SiO<sub>2</sub>. No metal was seen on top of the SiO<sub>2</sub>, and the Cu line was level with the SiO<sub>2</sub> space. Etch depth and anisotropic profile was consistent across varying feature sizes, as shown in Figure 4. The depth of Cu was kept greater than 70 nm, thick enough to serve as a substrate layer for surface-sensitive analysis techniques such as XPS. CHF<sub>3</sub> and Ar was chosen as the etch chemistry for its anisotropic etch profile. The gas mixture combines physical etching from Ar and chemical etching from CHF<sub>3</sub>. CHF<sub>3</sub> provides F radicals that etch SiO<sub>2</sub> [2,3]. Ar<sup>+</sup> ions etch the SiO<sub>2</sub> by breaking its crystal bonds. Ar<sup>+</sup> also desorbs the fluoropolymer film generated by the CHF<sub>2</sub> radicals, exposing horizontal surfaces to the etch gases [2]. The fluoropolymer keeps the etch directional, by passivating the sidewalls of the SiO<sub>2</sub> preventing lateral etching.

#### **Conclusions:**

We successfully developed a robust and reproducible process to fabricate patterned line and space wafers. The ability to perform experiments on a patterned wafer will greatly enhance our understanding of area selective deposition.

#### Acknowledgements:

Thanks to ERG and CNF staff for insight and helpful discussion. This work was performed in part at the Cornell NanoScale Facility via the 2019 CNF REU Program. The CNF is a member of the National Nanotechnology Coordinated Infrastructure (NNCI), which is supported by the National Science Foundation (Grant NNCI-1542081).

## **References:**

- [1] Mackus, A.J.M., M.J.M. Merkx, and W.M.M. Kessels. "From the Bottom-Up: Toward Area-Selective Atomic Layer Deposition with High Selectivity." Chemistry of Materials 31, no. 1: 2-12. https:// doi.org/10.1021/acs.chemmater.8b03454 (January 8, 2019).

- [2] Fuller, Lynn, "Plasma Etching", Microelectronic Engineering, Rochester Institute of Technology.

- [3] Kunimasa Takahashi, et al. 1994 Jpn. J. Appl. Phys. 33 4745.